تحكم إلكتروني جديد لأسس سلسلة / موازية لوسى لمحاكاة لأدوات الحث المؤرض

مايانك سريفاستافا قسم هندسة الالكترونيات والاتصالات، كيت، غازي أباد، الهند – 201206 الاتصال على البريد الإلكتروني: mayank2780@gmail.com

الخيلاصية

الهدف من هذه الورقة البحثية هو اقتراح سلسلة جديدة / موازية لوسي لمكونات الحث مؤرض مع الحد الأدنى من متطلبات العناصر النشطة والسلبية. كل دائرة محاكاة تم تقديمها توظف أحد الجهد عبر موصل مكبر للصوت (VDTA) جنبا إلى جنب مع مكثف واحد متصلا بالأرض. جميع نظم المحاكاة المقدمة هي محض خالية من المعادلات الحرة مع مرفق ضبط إلى جنب مع مكثف واحد متصلا بالأرض. جميع نظم المحاكاة المقدمة هي محض خالية من المعادلات الحرة مع مرفق ضبط الإلكترونية ولا تحتاج إلى أي شرط من مكونات مطابقة. في جميع التشكيلات المقترحة، تم تحقيق الاستخدام الكامل لمرحلة الإلكترونية ولا تحتاج إلى أي شرط من مكونات مطابقة. في جميع التشكيلات المقترحة، تم تحقيق الاستخدام الكامل لمرحلة الدلخلات من ADTA المستخدام الكامل لمرحلة مع مرفق ضبط من مكونات مطابقة. وي جميع التشكيلات المقترحة، تم تحقيق الاستخدام الكامل لمرحلة على مثالية ولا تحتاج إلى أي شرط من مكونات مطابقة. في جميع التشكيلات المقترحة، م تحقيق الاستخدام الكامل لمرحلة على من ملوف من مكونات مطابقة. وي جميع التشكيلات المقترحة، م تحقيق الاستخدام الكامل لمرحلة مع مرفق ضبط من مكونات مطابقة. وي جميع التشكيلات المقترحة، م تحقيق الاستخدام الكامل لمرحلة المدخلات من ADTA المستخدمة، باستثناء سلسلة واحدة AL. ويدرس أيضا أداء تكوينات المحاكاة المقدمة في ظل ظروف غير مثالية وكذلك مع المقاومة الطرفية من (NDTA). يتم تأكيد سلوك السلسلة المقترحة / موازية LR مع والوائر المقاومة من محقل المعابية معن الأمثلة. وقد تم التحقق من صحة التحليل النظري من خلال تشغيل محاكاة SPICE مع SPICE مع CMOS وم 0.18 مي مواد 0.18 مي مواد 1.18 مي مواد 0.18 مي مواد 1.18 مي مواد 0.18 مي مواد 1.18 مي مواد 0.18 مي مواد 0.18 مي مواد 1.18 مي معن الموابية من محمل مواد ما مي مواد ما مي معالية من محمل معان المولي من خلال تشغيل محاكاة مع SPICE مع SPICE مع SPICE مع SPICE مع SPICE مي مواد 0.18 مي مواد ما مولية مي مواد ما مولية مي مواد ما مولي مي مولال مي مولي مي مولال تشغيل محاكاة SPIC مي مولي مي مواد 0.18 مي مواد 0.18 مي مواد 0.18 مي مواد ما مولي مي مولي مي

# Novel electronically controllable grounded series/parallel lossy inductor simulator configurations

#### Mayank Srivastava

D/O Electronics and Communication Engineering, KIET, Ghaziabad (U.P.)201206, India E-mail: mayank2780@gmail.com

#### ABSTRACT

The objective of this research paper is to propose novel series/parallel lossy grounded inductor simulation configurations with the minimum requirement of active and passive elements. Each presented simulator circuit employs one voltage differencing transconductance amplifier(VDTA) along with a single capacitor connected to ground. All the presented simulators are purely resistor-free realizations with electronic tuning facility and do not need any requirement of component matching. In all the proposed configurations, full utilization of the input stage of employed VDTAs has been achieved, except forone series LR circuit. The performance of the presented simulation configurations is also studied under non-ideal conditions as well as with the terminal parasitic impedances of VDTA. The behavior of the proposed series/parallel R-L impedance simulation circuits is confirmed by some application examples. The theoretical analysis has been validated by running SPICE simulations with TSMC CMOS 0.18 µm process parameters.

**Keywords:** Electronic tuning; grounded capacitor; lossy inductor simulator; no component matching; single capacitor.

#### INTRODUCTION

Inductor is a popular member of the passive element family, which find several applications in electrical engineering. A conventional inductor is a spiral inductor, which unfortunately exhibits many disadvantageous features such as huge size and large weight, generation ofundesired harmonics of original signal, radiation of electromagnetic signals, and linear dependence of quality factor on the dimensions that are restricted to the design of an inductor with high quality factor and small size. Hence, in the last two decades, the interest has been comprehensively directed towards the realization of active element based configurations, which can simulate the behavior of passive conventional inductors. Some grounded/floating inductance simulation circuits using different active components have been reported in Prescottet al.(1966); Senani et al.(1978); Senani et al.(1978); Arslan et al.(2003); Yuce et al.(2008); Prasad et al.(2010); Kacaret al.(2010); Prasad et al.(2012) and reference-cited therein. In addition to the simulation of pure inductances, the simulation of lossy inductors is also a popular research area recently. The lossy grounded inductor simulators have broad range of applications in active filters, sinusoidal oscillators, and series/parallel resonance circuits. Numerous grounded series/parallel R-L circuit simulation configurations employing different active components have been available in the literature (Ford et al., 1966; Nandi et al., 1977; Nandi et al., 1978; Soliman et al., 1979; Nandi et al., 1979; Paulet al.,1981; Liu et al.,1994; Wang et al., 1998; Cam et al., 2004; Incekaraogluet al., 2005; Yuceet al., 2006; Yuceet al., 2006; Yuceet al., 2009; Kumar et al., 2010; Kacaret al., 2011; Metinet al., 2011; Kacaret al., 2014). Unluckily, all these proposed simulation circuits experience one or more of the following disadvantages: (i) employment of more than one active element; (ii) requirement of more than one capacitors; (iii) use of passive elements in floating states, which is not suitable for monolithic integration; (iv) unavailability of electronic tuning; (v) lack of non-interactive tuning of equivalent inductance; and (vi) need for passive component matching. Therefore, the objective of this research paper is to report some new series/parallel R-L grounded impedance simulators with the following useful features: (i) minimum need of active and passive elements ( one VDTA and onecapacitor); (ii) employment ground connected capacitor; (iii) no requirement of any external resistance; (iv) availability of electronic tuning facility; (v) availability of non-interactive tuning of realized inductance; (vi) no element matching constraints; and (vii) no deviation in behavior in non-ideal environment.

#### THE PROPOSED CONFIGURATIONS

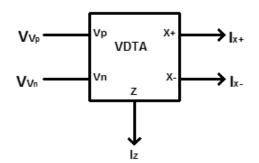

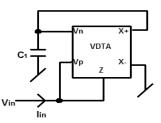

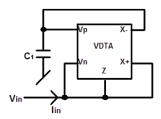

VDTA is a versatile modern active building block (ABB) (Bioleket al., 2008), finding many applications in designing of active filters (Prasad et al., 2013; Prasad et al., 2013), sinusoidal oscillators (Prasad et al., 2013; Srivastava et al., 2014), and inductance simulation configuration (Prasad et al., 2012). The electrical symbolic representation of VDTA has been illustrated in Figure 1, where two voltage input terminals are VP and VN and threeoutput ports are Z, X+ and X-. All the ports of VDTA are high impedance ports. The implementation of VDTA using CMOS technology has been proposed by Yesil in 2011 (Yesilet al., 2011).

Figure 1. Electrical symbolic representation of VDTA.

The current-voltage relationships between different ports of VDTA can be described by the following hybrid matrix equation set.

$$\begin{bmatrix} I_Z \\ I_{X^+} \\ I_{X^-} \end{bmatrix} = \begin{bmatrix} g_{m_1} & -g_{m_1} & 0 \\ 0 & 0 & g_{m_2} \\ 0 & 0 & -g_{m_2} \end{bmatrix} \begin{bmatrix} V_P \\ V_N \\ V_Z \end{bmatrix}$$

(1)

Fig. 2(b)

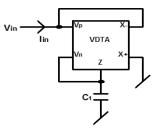

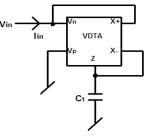

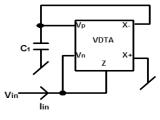

The proposed grounded series/parallel R-L impedance simulators are shown in Figure 2.

Fig. 2(d)

Figure 2. Proposed grounded series/parallel R-L simulators.

The input impedances, equivalent inductances, and equivalent resistances of the proposed circuit are given in Table 1, where "s" is a Laplace operator.

| Figure No. | Input impedance                                                    | Equivalent                  | Equivalent                | Туре                    |

|------------|--------------------------------------------------------------------|-----------------------------|---------------------------|-------------------------|

|            | $(\mathbf{Z}_{eq} = \mathbf{s} \mathbf{L}_{eq} + \mathbf{R}_{eq})$ | inductance                  | resistance                |                         |

|            |                                                                    | (L <sub>eq</sub> )          | (R <sub>eq</sub> )        |                         |

| Fig. 2(a)  | $Z_{eq} = \frac{sC_1}{g_{m1}g_{m2}} + \frac{1}{g_{m2}}$            | $\frac{sC_1}{g_{m1}g_{m2}}$ | $\frac{1}{g_{m2}}$        | +L series with +R       |

| Fig. 2(b)  | $Z_{eq} = \frac{sC_1}{g_{m1}g_{m2}} + \frac{1}{g_{m1}}$            | $\frac{sC_1}{g_{m1}g_{m2}}$ | $\frac{1}{g_{m1}}$        | +L series with +R       |

| Fig. 2(c)  | $Z_{eq} = \frac{1}{\frac{g_{m1}g_{m2}}{sC_1} + g_{m1}}$            | $\frac{sC_1}{g_{m1}g_{m2}}$ | $\frac{1}{g_{m1}}$        | +L parallel with<br>+R  |

| Fig. 2(d)  | $Z_{eq} = \frac{1}{\frac{g_{m1}g_{m2}}{sC_1} - g_{m1}}$            | $\frac{sC_1}{g_{m1}g_{m2}}$ | $-\frac{1}{g_{m1}}$       | +L parallel with -<br>R |

| Fig. 2(e)  | $Z_{eq} = \frac{1}{\frac{g_{m1}g_{m2}}{sC_1} + g_{m1} - g_{m2}}$   | $\frac{sC_1}{g_{m1}g_{m2}}$ | $\frac{1}{g_{m1}-g_{m2}}$ | +L parallel with<br>±R  |

Table 1. Proposed series/parallel R-L configurations.

One can observe from Table 1 that the proposed circuits can simulate series realization of (+R) with (+L) and parallel realizations of (+R) with (+L), (-R) with (+L), and (±R) with (+L). From the expressions of  $L_{eq}$  and  $R_{eq}$  it is clear that, in all the configurations, both  $L_{eq}$  and  $R_{eq}$  are electronically tunable by  $g_{m1}$  and/or  $g_{m2}$ . The circuits of Fig. 2(a), 2(b), and 2(c) provide independent control of Leq by  $g_{m1}$  and circuit of Fig. 2(d) by  $g_{m2}$  without disturbing  $R_{eq}$ . In the configuration shown in Fig. 2 (e),  $R_{eq}$  can be positive or negative depending upon the values of  $g_{m1}$  and  $g_{m2}$ . Hence, this configuration can be used as a parallel (+R)-(+L) circuit by taking  $g_{m1}$  larger than  $g_{m2}$  or (-R)-(+L) circuit by setting up gm1 smaller than gm2. The values of  $g_{m1}$  and  $g_{m2}$  can be adjusted easily by changing the bias currents of VDTA. Hence, the nature of this configuration can be changed electronically.

#### NON-IDEAL ANALYSIS

In a non-ideal environment, the current-voltage relations between different terminals of VDTA can be defined using the below given current-voltage equations:

$$I_Z = \beta_Z g_{m_1} \left( V_P - V_N \right) \tag{2}$$

$$I_{X+} = \beta_{x+} g_{m_2} V_Z \tag{3}$$

$$I_{X-} = \beta_{X-} g_{m_2} V_Z \tag{4}$$

where  $\beta_7$ ,  $\beta_{x_+}$  and  $\beta_{x_-}$  are the errors in transconductance gains under non-ideal conditions.

To examine the performance of the presented simulators under non-ideal environment, these configurations are revisited with non-ideal current-voltage Equations (2)-(4). The input impedances, equivalent inductances, and equivalent resistances of proposed circuits under non- ideal conditions are given in Table 2.

| Figure    | Input impedance                                                                                     | Equivalent                                                                                   | Equivalent                                     | Туре        |

|-----------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------|-------------|

| No.       | $(\mathbf{Z}_{eq} = \mathbf{L}_{eq} + \mathbf{R}_{eq})$                                             | inductance                                                                                   | resistance                                     |             |

|           |                                                                                                     | (L <sub>eq</sub> )                                                                           | (R <sub>eq</sub> )                             |             |

| Fig. 2(a) | $sC_1$ 1                                                                                            | $sC_1$                                                                                       | 1                                              | +L series   |

|           | $Z_{eq} = \frac{sC_1}{g_{m1}g_{m2}\beta_Z\beta_{X+}} + \frac{1}{g_{m2}\beta_{X+}}$                  | $g_{m1}g_{m2}\beta_Z\beta_{X+}$                                                              | $g_{m2}eta_{X+}$                               | with +R     |

| Fig. 2(b) | sC B                                                                                                | sC.                                                                                          | $\beta_{X-}$                                   | +L series   |

|           | $Z_{eq} = \frac{sC_1}{g_{m1}g_{m2}\beta_Z\beta_{X+}} + \frac{\beta_{X-}}{g_{m1}\beta_Z\beta_{X+}}$  | $\frac{g_{m1}g_{m2}\beta_{Z}\beta_{Z}\beta_{X+}}{g_{m1}g_{m2}\beta_{Z}\beta_{Z+}\beta_{X+}}$ | $\frac{P_{X^{-}}}{g_{m1}\beta_Z\beta_{X^{+}}}$ | with +R     |

| Fig. 2(c) | 1                                                                                                   | sC                                                                                           | 1                                              | +L parallel |

|           | $Z_{eq} = \frac{1}{\frac{g_{m1}g_{m2}\beta_{Z}\beta_{X-}}{sC_{1}} + g_{m1}\beta_{Z}}$               | $\frac{sC_1}{g_{m1}g_{m2}\beta_Z\beta_{X-}}$                                                 | $\frac{1}{g_{m1}\beta_Z}$                      | with +R     |

| Fig. 2(d) | 1                                                                                                   | $sC_1$                                                                                       | 1                                              | +L parallel |

|           | $Z_{eq} = \frac{1}{\frac{g_{m1}g_{m2}\beta_{Z}\beta_{X+}}{sC_{1}} - g_{m1}\beta_{Z}}$               | $\frac{sC_1}{g_{m1}g_{m2}\beta_Z\beta_{X+}}$                                                 | $-\overline{g_{m1}\beta_Z}$                    | with -R     |

| Fig. 2(e) | 1                                                                                                   | $sC_1$                                                                                       | 1                                              | +L parallel |

|           | $Z_{eq} = \frac{\frac{1}{g_{m1}g_{m2}\beta_Z\beta_{X-}}}{sC_1} + g_{m1}\beta_Z - g_{m2}\beta_{X+}}$ | $g_{m1}g_{m2}\beta_Z\beta_{X-}$                                                              | $\frac{1}{g_{m1}\beta_Z - g_{m2}\beta_{X+}}$   | with ±R     |

| Table 2. Proposed | series/parallel R-L | configurations u | under non-ide | al conditions. |

|-------------------|---------------------|------------------|---------------|----------------|

|                   |                     |                  |               |                |

On comparing the expression of Table 1 with Table 2, it can be illustrated that the behavior of the proposed simulators under non-ideal conditions remains the same as the ideal behavior. The values of Req and Leq are deviated from ideal values, but as the values of  $\beta x$ +,  $\beta x$ - and  $\beta z$  are very near to unity, deviations in Req and Leq are very minor. Hence, under non-ideal conditions, the performance of the proposed simulators matches closely with the ideal performance.

### **EFFECTS OF PARASITICS**

In this section, the behavior of the proposed series/parallel grounded R-L impedance simulators is evaluated in the presence of parasitic impedances of VDTA terminals. In VDTA realization, using CMOS (Yesilet al., 2011), finite grounded parasitic resistances come into viewat P, N, and Z ports, while finite grounded parasitic capacitances appear at X+, X-, and Z ports.

The quivalent circuits of the presented grounded series/parallel R-L circuit simulators considering the terminal parasitic impedances of VDTA have been given in Table 3.

| Influence of parasitics | $R_{A} = \frac{\left(\frac{1}{R_{Z}} + g_{m2}\right)}{\left(g_{m1}g_{m2}\right)}, L_{A} = \frac{\left(C_{1} + C_{z} + C_{n}\right)}{\left(g_{m1}g_{m2}\right)}$                                                                                 |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | $R_{A} = \frac{\left(\frac{1}{R_{Z}} + g_{m2}\right)}{\left(g_{m1}g_{m2}\right)}, L_{A} = \frac{\left(C_{1} + C_{z} + C_{n}\right)}{\left(g_{m1}g_{m2}\right)}$                                                                                 |

|                         |                                                                                                                                                                                                                                                 |

|                         | $R_{A} = \frac{\left(\frac{1}{R_{x-}} + \frac{1}{R_{z}} + g_{m2}\right)}{\left(g_{m1}g_{m2}\right)}, \ L_{A} = \frac{\left(C_{1} + C_{z}\right)}{\left(g_{m1}g_{m2}\right)}$                                                                    |

|                         | $R_{A} = \frac{\left(\frac{1}{R_{x-}}\right)}{\left(g_{m1}g_{m2}\right)}, \ L_{A} = \frac{\left(C_{1} + C_{p}\right)}{\left(g_{m1}g_{m2}\right)}, \ R_{B} = \frac{1}{\left(\frac{1}{R_{z}} + g_{m1}\right)},$                                   |

|                         | $C_A = C_z + C$                                                                                                                                                                                                                                 |

|                         | $R_{A} = \frac{\left(\frac{1}{R_{x+}}\right)}{\left(g_{m1}g_{m2}\right)}, \ L_{A} = \frac{\left(C_{1} + C_{n}\right)}{\left(g_{m1}g_{m2}\right)}, \ R_{B} = \frac{1}{\left(\frac{1}{R_{z}} + g_{m1}\right)},$                                   |

|                         | $C_A = C_z + C_p$                                                                                                                                                                                                                               |

|                         | $R_{A} = \frac{\left(\frac{1}{R_{x-}}\right)}{\left(g_{m1}g_{m2}\right)}, \ L_{A} = \frac{\left(C_{1} + C_{p}\right)}{\left(g_{m1}g_{m2}\right)},$ $R_{B} = \frac{1}{\left(\frac{1}{R} + \frac{1}{R} + g_{m1}\right)}, \ C_{A} = C_{z} + C_{n}$ |

|                         |                                                                                                                                                                                                                                                 |

Table 3. Equivalent circuits of the proposed configurations under the influence of VDTA parasitics.

# **APPLICATION EXAMPLES**

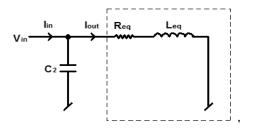

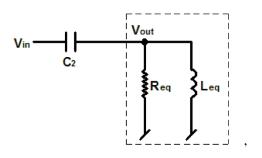

The configurations shown in Fig. 2(a), 2(c), and 2(d) are chosen as examples to confirm the working potential of the proposed series/parallel R-L impedance simulators by constructing some application circuits using these configurations. To demonstrate the performance of series (+R)-(+L) circuit simulator presented in Fig.2(a), we use it in the structure of the second order current mode low-pass filter (LPF) shown in Fig.3(a).

Figure 3. Second order current mode low-pass filter: (a) passive realization; (b) active realization using series (+R)-(+L) simulator proposed in Fig. 2(a).

The current transfer function of LPF shown in Figure 3(b) is given by

$$\frac{I_{out}}{I_{in}} = \frac{g_{m1}g_{m2}}{s^2 C_1 C_2 + s C_2 g_{m1} + g_{m1} g_{m2}}$$

(5)

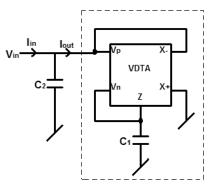

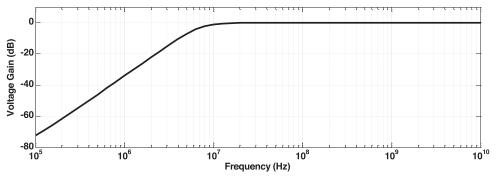

To examine the working of parallel (+R)-(+L) circuit simulator proposed in Fig. 2(c), a second order voltage mode high pass filter (HPF) has been designed as shown in Fig. 4(b).

Fig. 4(a)

Figure 4. Second order voltage mode high-pass filter; (a) realization using passive R-L-C: (b) active realization using parallel (+)R-(+L) simulator proposed in Fig. 2(c).

The frequency response of this HPF is shown in Figure 9. By routine analysis, the voltage transfer function of the realized HPF is given by

$$\frac{V_{out}}{V_{in}} = \frac{s^2 C_1 C_2}{s^2 C_1 C_2 + s C_1 g_{m1} + g_{m1} g_{m2}}$$

(6)

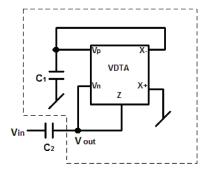

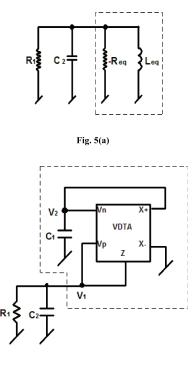

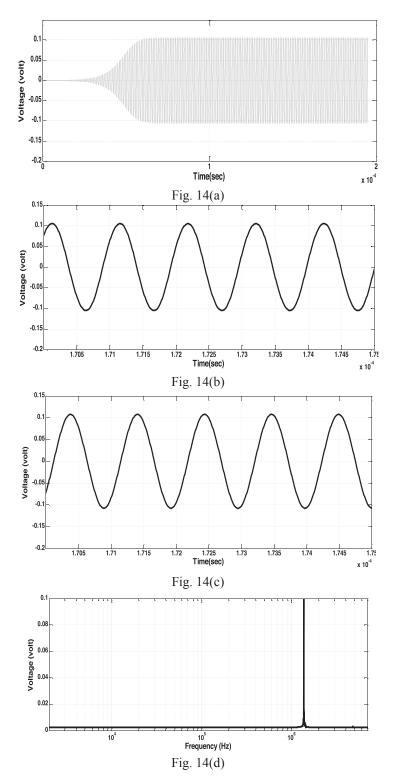

To illustrate the application of parallel (-R)-(+L) simulator shown in Fig. 2(d), it is used in construction of a second order oscillator as shown in Figure 5.

Fig. 5(b)

Figure 5. Second order oscillator; (a) passive realization: (b) active realization using parallel (-R)-(+L) simulator proposed in Fig. 2(d).

The condition of oscillation (CO) and frequency of oscillation (FO) of the oscillator given in Fig. 5(b) are

$$\frac{1}{R_{1}} - g_{m1} \le 0$$

(7)

$$\omega_{0} = \sqrt{\frac{g_{m1}g_{m2}}{C_{1}C_{2}}}$$

(8)

### SIMULATION RESULTS

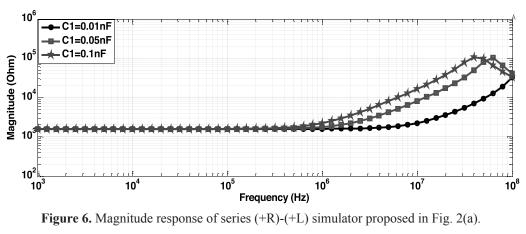

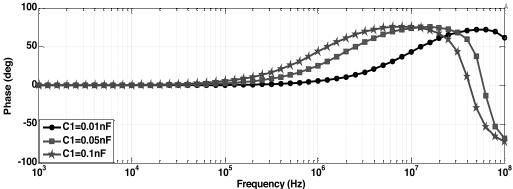

To validate the theoretical analysis, SPICE simulations were performed employing CMOS VDTA (Yesilet al., 2011). The DC supply voltages were chosenas±0.9 VDC with all the biasing currents of VDTA being equal to150  $\mu$ A. Series R-L simulator inFig.2(a) is simulated with C1=0.01nF, 0.05nF, and 0.1nF. The magnitude and phase responses of input impedance of the circuit, shown in Fig. 2(a), have been shown in Figures 6 and 7, respectively. From the input impedance expression of Fig. 2(a) given in table1, it can be seen that, for a high value of C<sub>1</sub>, the value of L<sub>eq</sub> is high in comparison to lossy part R<sub>eq</sub> and the behavior of this series lossy inductor becomes inclined more towards a lossless inductor. For further high values of C<sub>1</sub>, the value of R<sub>eq</sub> will be very small in comparison to L<sub>eq</sub> and the configuration will work like a pure lossless inductor. This effect can be illustrated by magnitude response plots shown in Figure 6 The initial "horizontal part" of frequency response is due to the existence of lossy term "R<sub>eq</sub>". As the value of

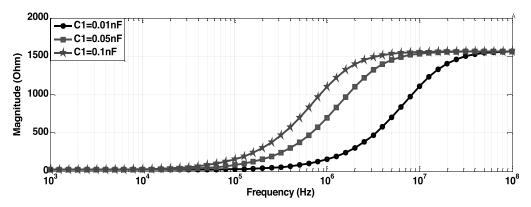

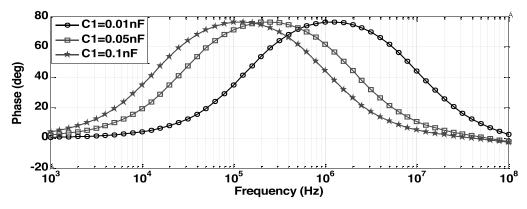

$C_1$  increases, the value of  $L_{eq}$  becomes high, and the flat part of response becomes comparatively narrower than remaining inclined, which clearly indicates that, on increasing "C<sub>1</sub>", the behavior of the proposed circuit starts inclining towards the behavior of lossless inductor. Parallel R-L simulator of Fig. 2(c) is also simulated with  $C_1$ =0.01nF, 0.05Nf, and 0.1nF. The magnitude and phase responses of the input impedance of this circuit have been shown in Figures 8 and 9. Figure8 shows that the input impedance magnitude is low for small values of "C<sub>1</sub>" and the curve is more flat, which can be verified by the mathematical expression given in Table 1.

Figure 7. Phase response of series (+R)-(+L) simulator proposed in Fig.2(a).

Figure 8. Magnitude response of parallel (+R)-(+L) simulator proposed in Fig. 2(c).

Figure 9. Phase response of parallel (+R)-(+L) simulator proposed in Fig. 2(c).

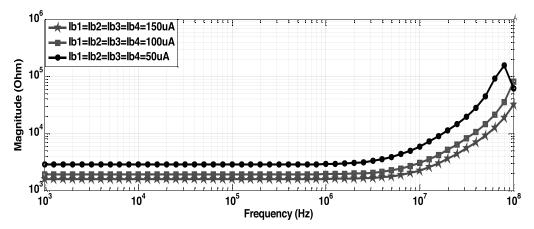

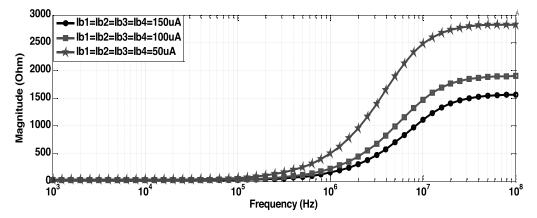

To show the electronic controllability facility in series R-L simulator shown in Fig.2(a), the simulation has been performed for a different set of bias current values with  $C_1=0.01$ nF. The simulation plots are shown in Figure10, which clearly illustrate that, on increasing the bias currents, the values of  $g_{m1}$  and  $g_{m2}$  are increasing and the input impedance is decreasing. Electronic tunability of parallel R-L simulator shown in Fig. 2(c) has been demonstrated in the plots shown in Figure11 selecting  $C_1=0.01$ nF.

Figure 10. Response of series (+R)-(+L) simulator shown in Fig. 2(a) for different bias currents.

Figure 11. Response of series (+R)-(+L) simulator proposed in Fig. 2(c) for different bias currents.

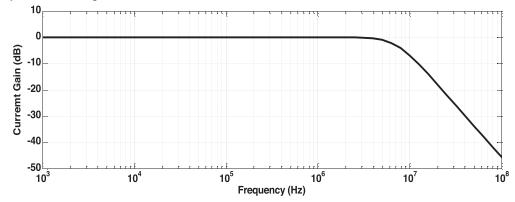

The realized LPF shown in Fig. 3(b) is simulated with passive component values selected as  $C_1=0.01$ nF and  $C_2=0.02$ nF. The simulated filter response is shown in Figure 12.

Figure 12. Frequency response of second order current mode low-pass filter shown in Fig. 3(b).

For simulation of high-pass filter shown in Fig. 4(b), the following component values are chosen:  $C_1=0.02$ nF and  $C_2=0.01$ nF. The frequency response of this high pass filter has been shown in Figure 13.

Figure 13. Frequency response of second order voltage mode high-pass filter shown in Fig. 4(b).

The passive elements' values used for the simulation of the oscillator shown in Fig. 5(b) are as follows:  $C_1=C_2=0.1$  nF and  $R_1=1.7$  k $\Omega$ . Fig. 14(a), 14(b), and 14(c) show the transient and steady state responses of voltage outputs  $V_1$  and  $V_2$ . The phase difference between  $V_1$  and  $V_2$  is found to be 89.67°, which confirms the quadrature phase relationship between  $V_1$  and  $V_2$ . Fig. 14(d) shows the frequency spectrum of voltage  $V_1$  where FO is found to be 1005.6 KHz, while the ideal value of FO is 1010 KHz. So, the simulated value is inclose agreement with the ideal value.

**Figure 14.** Responses of oscillator shown in Fig. 5(b):(a) transient response of V1 and V2;(b) steady state response of V1; (c) steady state response of V2; (d) frequency spectrum.

The comparison of the proposed grounded series/parallel R-L simulators with the previously proposed same type of circuits is given in Tables 4 and 5.

| Ref.                        | Fig. No.               | Number<br>of active<br>element | Number of resistor | Number of capacitor | Electronic control<br>of "Leq"and<br>"Req" | Non-Interactive control of "Leq" | Need of<br>element<br>matching |

|-----------------------------|------------------------|--------------------------------|--------------------|---------------------|--------------------------------------------|----------------------------------|--------------------------------|

| Nandiet al.,<br>1977        | Fig.2(a)               | 1                              | 1(F)+<br>1(G)      | 1(F)                | No                                         | No                               | No                             |

| Nandi et al.,<br>1978       | Fig. 1                 | 1                              | 1(F)+<br>1(G)      | 1(F)                | No                                         | No                               | No                             |

|                             | Fig. 2                 | 2                              | 1(F)+<br>1(G)      | 1(F)                | No                                         | Yes                              | No                             |

|                             | Fig. 2                 | 2                              | 2(F)+<br>1(G)      | 1(G)                | No                                         | Yes                              | No                             |

|                             | Fig. 2                 | 2                              | 1(F)+<br>1(G)      | 1(F)                | No                                         | Yes                              | No                             |

| Nandi et al.,<br>1979       | Fig.1(a),<br>Fig.1(b)  | 2                              | 2(F)+<br>2(G)      | 1(G)                | No                                         | Yes                              | Yes                            |

| Paul et al., 1981           | Fig. 1                 | 1                              | 2(F)+<br>2(G)      | 1(F)                | No                                         | Yes                              | Yes                            |

| Liuet al., 1994             | Fig. 1                 | 1                              | 1(F)+<br>1(G)      | 2(G)                | No                                         | Yes                              | Yes                            |

| Wang et al.,<br>1998        | Fig.2(b)               | 1                              | 1(F)+<br>1(G)      | 1(F)                | No                                         | No                               | No                             |

| Incekaraogluet<br>al., 2005 | Fig.2(a)               | 1                              | 1(F)+<br>1(G)      | 1(G)                | No                                         | No                               | No                             |

|                             | Fig.2(b)               | 1                              | 2(F)+<br>1(G)      | 1(F)                | No                                         | No                               | No                             |

| Yuce et al.,<br>2009        | Fig.2 –<br>Fig.5       | 1                              | 1(F)+<br>1(G)      | 1(F)                | No                                         | Yes                              | No                             |

| Kacaret al.,<br>2011        | Fig.2(b)               | 1                              | 1(F)+<br>1(G)      | 1(F)                | No                                         | No                               | No                             |

| Metinet al.,<br>2011        | Fig.2(b)               | 1                              | 2(F)               | 1(F)                | No                                         | Yes                              | No                             |

|                             | Fig. 2(f)              | 1                              | 2(F)+<br>1(G)      | 1(F)                | No                                         | No                               | No                             |

| Kacaret al.,<br>2014        | Fig.2(c) –<br>Fig.2(f) | 1                              | 1(G)               | 1(G)                | No                                         | Yes                              | No                             |

| Proposed                    | Fig.2(a),<br>Fig.2(b)  | 1                              | 0                  | 1-(G)               | Yes                                        | Yes                              | No                             |

Table 4. Comparison with previously proposed grounded series R-L circuit simulators.

G\* Grounded. F\* Floating

| Ref.                        | Fig. No.              | Number of      | Number of | Number of | Electronic control of both | Non-Interactive<br>control of | Need of element |

|-----------------------------|-----------------------|----------------|-----------|-----------|----------------------------|-------------------------------|-----------------|

| iter.                       | 1 ig. 100.            | active element | resistor  | capacitor | "Leq" and "Req"            | "Leq"                         | matching        |

| Ford et al.,<br>1966        | Fig.1(a)              | 1              | 2(F)      | 1(F)      | No                         | No                            | No              |

| Solimanet al.,<br>1979      | Fig.2(a)              | 1              | 1(F)      | 1(G)      | No                         | Yes                           | No              |

| Pauletal., 1981             | Fig.1                 | 1              | 2(F)+2(G) | 1(F)      | No                         | Yes                           | Yes             |

| Wang et al.,<br>1998        | Fig.2(a)              | 1              | 1(F)+1(G) | 1(F)      | No                         | Yes                           | No              |

| Cam et al.,<br>2004         | Fig.2(a),<br>Fig.2(b) | 2              | 4(F)      | 1(F)      | No                         | Yes                           | No              |

| Incekaraogluet<br>al., 2005 | Fig.3(a),<br>Fig.3(b) | 1              | 1(F)+1(G) | 1(G)      | No                         | No                            | No              |

| Yuceet al.,<br>2006         | Fig.3(a),<br>Fig.3(b) | 1              | 1(F)+1(G) | 1(F)      | No                         | No                            | No              |

| Yuceet al.,<br>2006         | Fig.2                 | 1              | 1(F)+1(G) | 1(G)      | No                         | No                            | No              |

| Kumar et al.,<br>2010       | Fig.1                 | 1              | 2(F)+2(G) | 1(F)      | No                         | No                            | No              |

| Kacaret<br>al.,2011         | Fig.2(c)              | 1              | 1(F)+1(G) | 1(F)      | No                         | Yes                           | No              |

| Metinet al.,<br>2011        | Fig.2(c)              | 1              | 2(F)+1(G) | 1(F)      | No                         | No                            | Yes             |

|                             | Fig.2(d)              | 1              | 3(G)      | 1(F)      | No                         | No                            | No              |

|                             | Fig.2(e)              | 1              | 2(F)+1(G) | 1(F)      | No                         | Yes                           | No              |

| Proposed                    | Fig.(2c),<br>Fig.2(d) | 1              | 0         | 1(G)      | Yes                        | Yes                           | No              |

|                             | Fig.2(e)              | 1              | 0         | 1(G)      | Yes                        | No                            | No              |

Table 5.Comparison with previously proposed grounded parallel R-L circuit simulators.

G\* Grounded. F\* Floating

## CONCLUSION

This paper proposes some new grounded series/parallel lossy inductor simulators using VDTA. All the presented configurations are very compact with a minimum requirement of active and passive elements (single VDTA and one capacitor). The proposed configurations have several profitable points such as the use of grounded capacitor, facility of electronic tuning, non-interactive tuning of equivalent inductance, and no need of any element value matching. To check the workability of the presented circuits, some application examples are given. SPICE simulations are included to confirm the theoretical analysis.

#### REFERENCES

- Prescott, A.J. 1966.Loss compensated active gyrator using differential input operational amplifier. Electronics Letters, 2(7): 283-284.

- Senani, R. 1978. Active simulation of inductors using current conveyors. Electronics Letters, 14(15): 483-484.

- Senani, R. 1978. New Tunable Synthetic Floating Inductors. Electronics Letters, 6(10): 382-383.

- Arslan E. Cam, U. &Cicekoglu, O. 2003. Novel lossless grounded inductance simulators employing only a single first generation current conveyor. Frequenz; journal of RF engineering and telecommunications 57: 204–206.

- Yuce, E. 2008. Grounded Inductor Simulators with Improved Low Frequency Performances. IEEE Trans. Instrumentation and Measurement, 57(5): 1079-1084.

- Prasad, D. Bhaskar, D.R. & Singh, A.K. 2010. New grounded and floating simulated inductance circuits using current differencing transconductance amplifiers. Radioengineering19(1): 194-198.

- Kacar, F.2010.New lossless inductance simulators realization using a minimum active and passive components.MicroelectronicsJournal, 41(2-3): 109-113.

- Prasad, D. & Bhaskar, D.R. 2012. Grounded and floating inductance simulation circuits using VDTAs. Circuits and Systems 3(4): 342-347.

- Ford, R.L. & Girling, F.E.G. 1966. Active filters and oscillators using simulated inductance Electronics Letters 2(2): 481–482

- Nandi, R.1977. Inductor Simulation Using a Current Conveyor. Proceedings of the IEEE, 65(10):1511-1512.

- Nandi, R.1978. Active inductances using current conveyors and their application in a simple bandpass filter realization. Electronics Letters, 14(12): 373-374.

- Soliman A.M.1979. Grounded inductance simulation using the DVCCS/DVCVS. Proc. of the IEEE, 66(9): 334-336.

- Nandi, R.1979.Insensitive grounded-capacitor simulation of grounded inductors using current conveyors. Electronics Letters, 15(21): 693-694.

- Paul, A.N. & Patranabis, D. 1981. Active simulation of grounded inductors using a single current conveyor. IEEE Trans. Circuits and Systems 28: 164-165.

- Liu, S.J. & Hwang, Y.S. 1994. Realisation of R-L and C-D impedances using a current feedback amplifier and its Applications. Electronics Letters, 3(5): 380-381.

- Wang, H.Y. &Lee, C.T.1998.Realisation of R-L and C-D immittances using single FTFN. Electronics Letters, 34(6): 502–503.

- Cam, U., Cicekoglu, O., Kuntman, H. &Kuntman, A.2004. Novel two OTRA-based grounded immitance simulator topology. Analog Integrated Circuits and Signal Processing, 39(2): 169–175.

- Incekaraoglu, M. &Cam, U.2005.Realization of series and parallel R-L and C-D impedances using single differential voltage current conveyor. Analog Integrated Circuits and Signal Processing, 43:101-104.

- Yuce, E., Minaei, S. &Cicekoglu, O.2006.Limitations of the simulated inductors based on a single current conveyor.IEEE Trans. Circuits and Systems,53(12): 2860-2867.

- Yuce, E.2006.Comment on "realization of series and parallel R-L and C-D impedances using single differential voltage current conveyor. Analog Integrated Circuits and Signal Processing, **49**: 91-92.

- Yuce, E.2009.Novel lossless and lossy grounded inductor simulators consisting of a canonical number of components. Analog Integrated Circuits and Signal Processing, 59: 77-82.

- Kumar, P. &Senani, R. 2010.New grounded simulated inductance circuit using a single PFTFN.Analog Integrated Circuits and Signal Processing 62(1): 105–112.

- Kacar F. &Kuntman, H. 2011.CFOA-based lossless and lossy inductance simulators.Radioengineering, 20(3): 627-631.

- Metin, B.2011.Supplementary inductance simulator topologies employing single DXCCII. Radioengineering, 20(3): 614-618.

- Kacar, F., Yesil, A., Minaei, S. &Kuntaman, H. 2014. Positive/negative lossy/lossless grounded inductance simulators employing single VDCC and only two passive elements. International Journal of Electronics and Communication (AEU), 68(1): pp. 73-78.

- BiolekD. Senani, R. Biolkova, V. &Kolka, Z. 2008. Active elements for analog signal processing; classification, review and new proposals. Radioengineering, 17(4): 15-32

- Yesil,A. Kacar, F. &Kuntman, H. 2011. New simple CMOS realization of voltage differencing transconductance amplifier and its RF filter application. Radioengineering, 20(3): 632-637.

- Prasad, D. Bhaskar, D.R. & Srivastava, M. 2013. Universal current-mode biquad filter using a VDTA. Circuits and Systems 4(1): 29-33.

- Prasad, D. Bhaskar D.R. & Srivastava, M. 2013. Universal voltage-mode biquad filter using voltage differencing transconductance amplifier. Indian Journal of Pure and Applied Physics 51(12): 864-868.

- Prasad, D. Srivastava, M. & Bhaskar, D.R. 2013. Electronically controllable fully uncoupled explicit current mode quadrature oscillator using VDTA and grounded capacitors. Circuits and Systems 4(2): 169-172.

- Srivastava, M., Prasad, D. &Bhaskar, D.R. 2014. Voltage mode quadrature oscillator employing single VDTA and grounded capacitors. Contemporary Engineering Sciences, 7(27): 1501-1507.